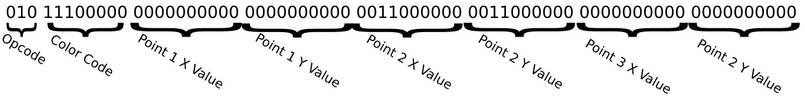

With the Bresenham Line Drawing implemented in Verilog last semester, the main goal for this semester was to take that implementation and generate triangle coordinates in a new Verilog program. This was done by creating two different scenarios, a flat bottom approach, and a flat top approach. Given three coordinates, with one side being a flat straight line, the Verilog program will then provide the coordinates needed for a triangle drawing.

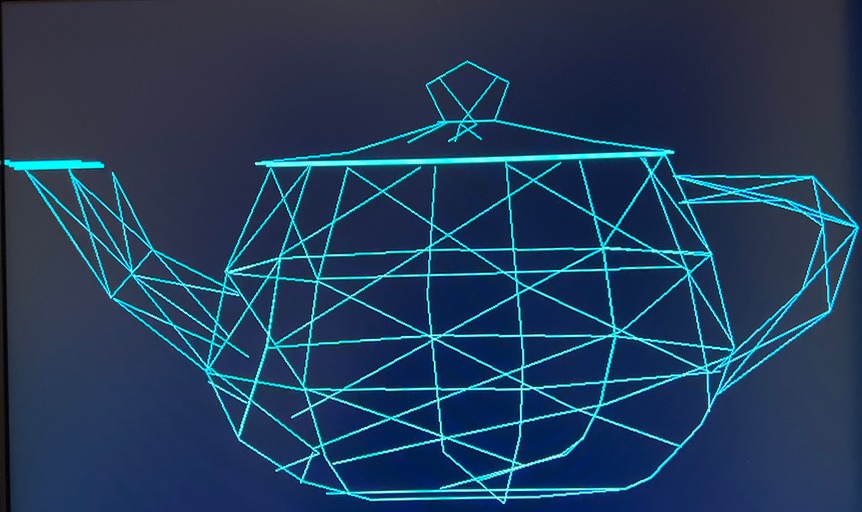

The figure shown below demonstrates the functioning triangle drawing program in our first successful demo run.