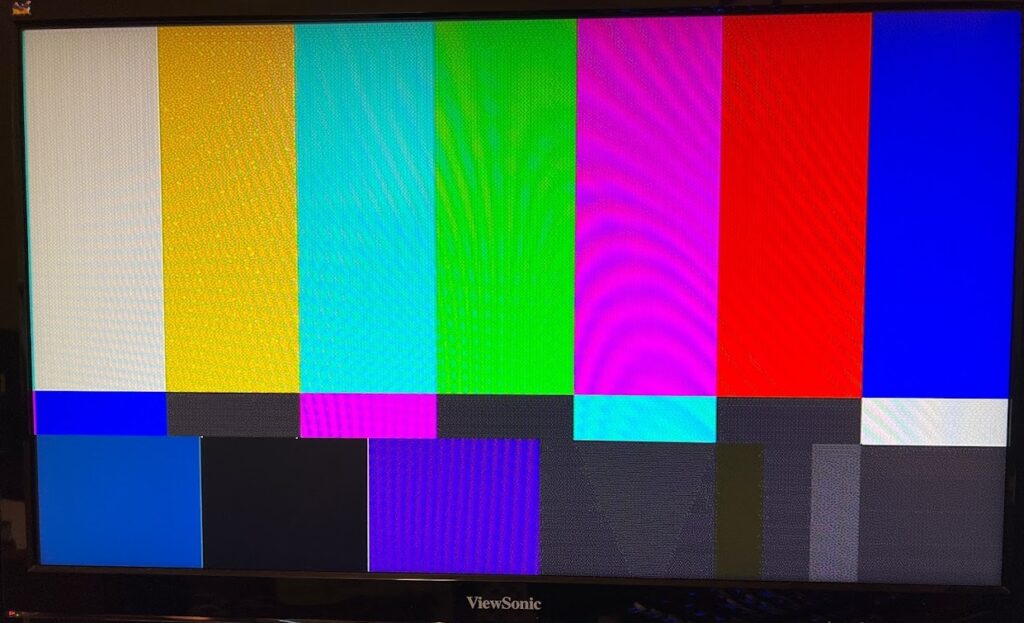

Implementing a frame buffer allows the display engine to output pixels as defined in memory. Using dual-port RAM, we can read and write at the same time.

Using a function to convert an x,y pixel address to a memory address, the display engine can directly retrieve pixel data with the frame buffer. The function for this is as follows:

MemoryAddress = Hcount + 800 * Vcount

Where Hcount and Vcount both start at 0 and increment until they reset. Loading the frame buffer with default data allows us to display a test pattern.